# DEUTERIUM IN THE GATE DIELECTRIC OF CMOS DEVICES

Albert Jan Hof

### Samenstelling promotiecommissie

Voorzitter:

prof. dr. W.H.M. Zijm

prof. dr. H. Wallinga

Secretaris:

prof. dr. W.H.M. Zijm Universiteit Twente

Promotor:

prof. dr. J. Schmitz Universiteit Twente

Assistent promotor:

dr. A.Y. Kovalgin Universiteit Twente

Deskundige:

dr. P.H. Woerlee Philips Research Laboratories

Leden:

prof. dr. ir. F.G. Kuper Universiteit Twente

Philips Semiconductors Universiteit Twente

prof. dr. J.H.W. de Wit Technische Universiteit Delft

TNO

Title: Deuterium in the Gate Dielectric of CMOS Devices

Author: Albert Jan Hof ISBN: 90-365-2093-2

This research has been supported by Philips Semiconductors.

## DEUTERIUM IN THE GATE DIELECTRIC OF CMOS DEVICES

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. F.A. van Vught, volgens besluit van het College voor Promoties in het openbaar te verdedigen op vrijdag 29 oktober 2004 om 13.15 uur

$\operatorname{door}$

Albert Jan Hof

geboren op 11 augustus 1976

te Wolvega

Dit proefschrift is goedgekeurd door:

de promotor prof. dr. J Schmitz de assistent promotor dr. A.Y. Kovalgin.

## Contents

| C              | onte              | nts                                  | i             |

|----------------|-------------------|--------------------------------------|---------------|

| $\mathbf{S}$ ι | ımm               | ary                                  | iii viii  1 7 |

| Sa             | men               | vatting                              | vii           |

| 1              | Inti              | $\operatorname{roduction}$           | 1             |

| 2              | <b>We</b> : 2.1   | t oxidation of silicon Introduction  |               |

|                | $\frac{2.1}{2.2}$ | Existing silicon oxidation models    |               |

|                | 2.3               | Experimental setup                   |               |

|                | 2.4               | Results and discussion               | _             |

|                | 2.5               | Conclusions                          |               |

| 3              | Nev               | w oxidation model                    | 25            |

|                | 3.1               | Introduction                         | 25            |

|                | 3.2               | Initial oxidation regime             | 26            |

|                | 3.3               | Electron tunnelling                  | 27            |

|                | 3.4               | New oxidation mechanism              | 28            |

|                | 3.5               | Verification of the new model        | 31            |

|                | 3.6               | Conclusions                          | 32            |

| 4              | Dev               | vice fabrication                     | 33            |

|                | 4.1               | Introduction                         | 33            |

|                | 4.2               | General CMOS manufacturing           | 34            |

|                | 4.3               | Hydrogen-containing processing steps | 37            |

|                | 4.4               | Hydrogen diffusion                   | 39            |

|                | 4.5               | Devices fabricated at the university | 40            |

|                | 4.6               | Devices fabricated by Philips        | 42            |

#### Contents

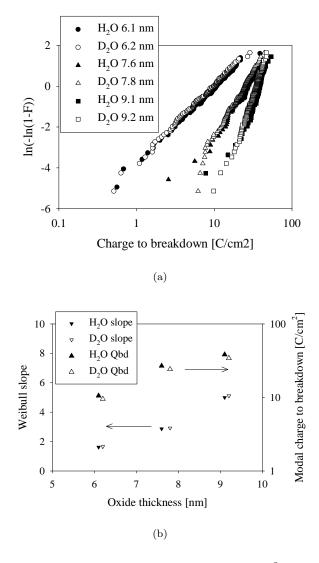

| 5  | Bul               | k quality                          |  |  |  |  |

|----|-------------------|------------------------------------|--|--|--|--|

|    | 5.1               | Introduction                       |  |  |  |  |

|    | 5.2               | Field-assisted tunnelling          |  |  |  |  |

|    | 5.3               | The impact of FN-tunnelling stress |  |  |  |  |

|    | 5.4               | Work by others                     |  |  |  |  |

|    | 5.5               | Experimental setup                 |  |  |  |  |

|    | 5.6               | Results                            |  |  |  |  |

|    | 5.7               | Discussion                         |  |  |  |  |

|    | 5.8               | Conclusions                        |  |  |  |  |

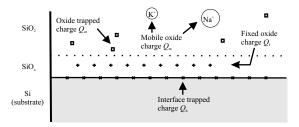

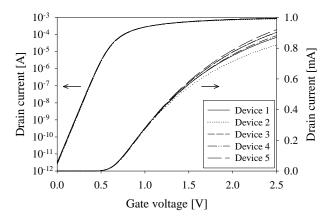

| 6  | Interface quality |                                    |  |  |  |  |

|    | 6.1               | Introduction                       |  |  |  |  |

|    | 6.2               | Silicon oxide charges              |  |  |  |  |

|    | 6.3               | Impact of hot carrier stress       |  |  |  |  |

|    | 6.4               | Work by others                     |  |  |  |  |

|    | 6.5               | Experimental setup                 |  |  |  |  |

|    | 6.6               | Results                            |  |  |  |  |

|    | 6.7               | Discussion and conclusions         |  |  |  |  |

| 7  | Cor               | nclusions                          |  |  |  |  |

| Aj | ppen              | dix                                |  |  |  |  |

| Bi | bliog             | graphy                             |  |  |  |  |

| Da | ankw              | voord                              |  |  |  |  |

| Li | st of             | publications                       |  |  |  |  |

| Δ1 | oout              | the author                         |  |  |  |  |

### Summary

Most of the electronic integrated circuits used today are Complementary MOS (CMOS) circuits, which consist mainly of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs). In the last forty years there has been a tremendous reduction of the MOSFET dimensions. This reduction will continue, enabling even faster and more complex integrated circuits. But, there are a number of hurdles on the road. One of these hurdles is the thickness reduction of an essential electrically isolating layer inside the MOSFET, the so-called gate dielectric. This gate dielectric is becoming so thin, it starts to leak electrical current under operating conditions. This increases the power consumption and can lead to a non-functional transistor. Reliability is also of concern, because the gate dielectric deteriorates under device operation, leading to even larger leakage currents.

The degradation of the gate dielectric is due to the creation of defects in its bulk and at its interface with the substrate underneath. Hydrogen is believed to play a crucial role in this. Some reports in literature suggest that replacing hydrogen with its isotope deuterium during device fabrication can improve the resistance to degradation. This claim is investigated in this thesis. The gate dielectric used throughout this thesis is silicon oxide.

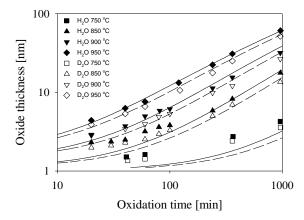

The most direct method to incorporate deuterium is during the growth of the gate dielectric, using a deuterated ambient. To this means, silicon oxidation data, *i.e.* oxide thickness as a function of oxidation time, has been obtained for silicon oxidation in ultra-diluted (partial pressure  $0.7\,\mathrm{kPa}$ )  $\mathrm{H_2O}$  and  $\mathrm{D_2O}$  ambient at different temperatures. The oxidation data shows that the silicon oxidation rate in a  $\mathrm{D_2O}$  ambient is 18 % lower than in a  $\mathrm{H_2O}$  ambient. This is independent of oxidation time and oxide thickness. A difference of 15 to 17 meV in activation energy suffices to give a change of 18 % in oxidation rate in the investigated temperature range of 750 to 950 °C. An

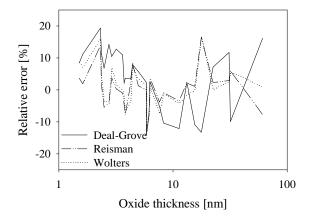

attempt to model the obtained oxidation data with existing physical oxidation models is not satisfactory. The Deal-Grove, Reisman and Wolters model are equally good in describing the data. Since the Reisman and Wolters model do not specify how the model parameters depend on oxidation temperature and pressure, the Deal-Grove model is preferred. However, the parameter values needed to fit the Deal-Grove model to the obtained data are not in accordance with values reported in literature and the relative error still remains in the range of 20 \%. In this thesis, a new silicon oxidation model has been developed, taking into account electron-stimulated dissociation of the oxidising species and the out-diffusion of the dissociated species. It is a full physical model with a limited number of parameters. The model is able to fit the silicon oxidation data within 30% accuracy. It is expected that this can be improved if the electron-dissociated stimulation is not only taken to occur at the SiO<sub>2</sub> surface and the Si-SiO<sub>2</sub> interface, but also in the bulk of the silicon oxide.

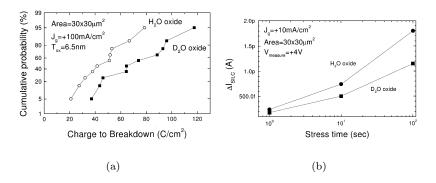

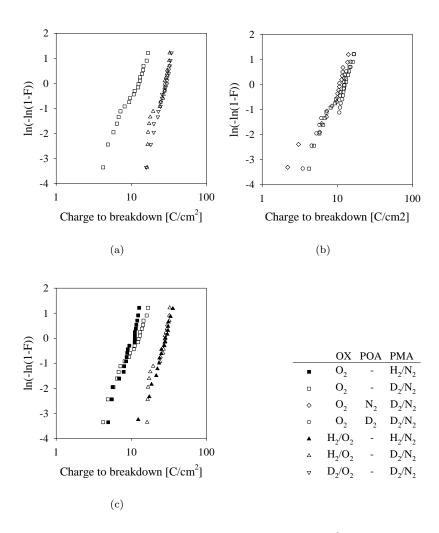

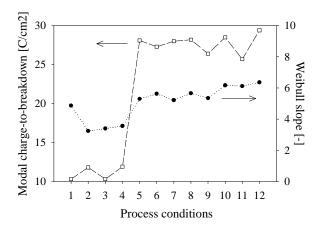

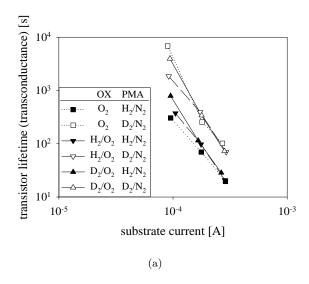

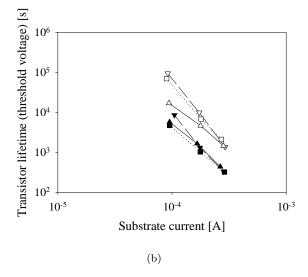

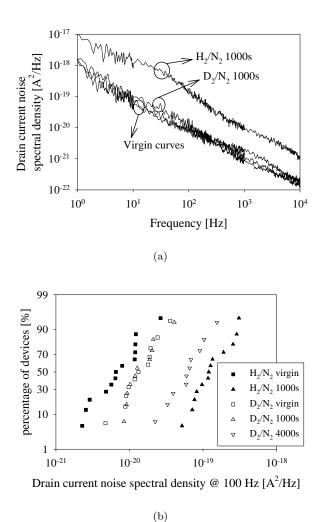

The obtained knowledge on the oxidation kinetics of silicon in a deuterated ambient has been used to fabricate CMOS devices with deuterium in the gate dielectric. Deuterium has also been introduced during other processing steps. Measurements regarding the bulk quality of the gate dielectric of these devices show no improvement of the resistance to degradation. Deuterated gate dielectrics degrade as fast as hydrogenated gate dielectrics under Fowler-Nordheim stressing conditions. This is independent of the processing stage in which deuterium was introduced. The results are well acceptable in view of our current understanding of SiO<sub>2</sub> degradation, but do contradict with several experimental observations reported in literature. On the other hand, measurements regarding the interface quality, do show an improvement of the resistance to degradation. However, this only occurs when the deuterium is introduced during the post-metal anneal at the end of the process. Earlier incorporation of deuterium does not show improved resistance to hot carrier degradation. Most likely, because the early introduced deuterium is replaced with hydrogen during high temperature processing steps that follow the step introducing deuterium. Hydrogen is abundantly available in CMOS manufacturing, so this is a plausible idea.

In conclusion, it can be stated that for deuterium to be beneficial for CMOS devices, it has to be incorporated at the end of the CMOS manufacturing process, to avoid replacement with hydrogen. The only benefit will be a higher resistance to hot carrier degradation. This will allow for higher internal electric fields in the CMOS devices.

Hot carrier degradation has been a primary reason for reduction of the supply voltage. The incorporation of deuterium can relax this demand for a decreased supply voltage.

### Samenvatting

De meeste huidige geïntegreerde schakelingen zijn Complementaire MOS (CMOS) schakelingen, welke hoofdzakelijk bestaan uit veldeffect transistoren, de zogenaamde MOSFETs. Gedurende de laatste veertig jaar zijn de afmetingen van deze MOSFETs enorm gereduceerd. Deze reductie gaat voorlopig nog door en maakt nog snellere en meer complexe schakelingen mogelijk. Maar er zijn een aantal obstakels. Eén van deze obstakels is de reductie van de dikte van een essentieel elektrisch isolerend laagje in de MOSFET, het zogenaamde gate-diëlektricum. Dit gate-diëlektricum wordt zo dun, dat er elektrische stroom doorheen begint te lekken onder gebruikerscondities. Dit verhoogt de energieconsumptie en kan tot niet-functionele transistoren leiden. Een ander heikel punt is de betrouwbaarheid. Tijdens gebruik 'slijt' het gate-diëlektricum als het ware, wat leidt tot nog grotere lekstromen.

De degradatie van het gate-diëlektricum wordt veroorzaakt door het ontstaan van defecten zowel in het gate-diëlektricum als op het grensvlak van het gate-diëlektricum met het onderliggende substraat. Er wordt verondersteld dat waterstof hierin een cruciale rol speelt. In een aantal wetenschappelijke artikelen wordt gesteld dat het vervangen van waterstof met diens isotoop deuterium tijdens de fabricage van de MOSFETs de weerstand tegen degradatie kan verhogen. Deze claim is nader onderzocht in dit proefschrift. Het gate-diëlektricum dat gebruikt wordt in dit proefschrift is siliciumoxide.

De meest directe manier om deuterium in te brengen, is tijdens de groei van het gate-diëlektricum, in een gedeutereerde omgeving. Hiertoe is data over de oxidatie van silicium, d.w.z. oxidedikte tegen oxidatietijd, vergaard voor siliciumoxidatie in een ultra-verdunde (partieel druk  $0.7\,\mathrm{kPa}$ )  $\mathrm{H_2O}$  en  $\mathrm{D_2O}$  omgeving bij verschillende oxidatietemperaturen. De oxidatiedata laat zien dat de snelheid van siliciumoxidatie in een  $\mathrm{D_2O}$  omgeving  $18\,\%$  lager is dan in een  $\mathrm{H_2O}$

omgeving. Dit is onafhankelijk van de oxidatietijd en oxidedikte. Een verschil van 15 tot 17 meV in activeringsenergie is voldoende om het verschil van 18 % te verklaren in het onderzochte temperatuurbereik van 750 tot 950 °C. De modellering van de verkregen oxidatiedata met bestaande modellen van siliciumoxidatie is niet toereikend. De modellen van Deal en Grove, Reisman en Wolters zijn alle even goed in staat om de data te beschrijven. Het model van Deal en Grove verdient de voorkeur, aangezien de modellen van Reisman en Wolters niet specificeren hoe de modelparameters afhangen van de oxidatietemperatuur en -druk. Echter, de parameterwaarden die nodig zijn voor het model van Deal en Grove om de verkregen data te beschrijven zijn niet in overeenstemming met de waarden uit de vakliteratuur. Bovendien blijft de relatieve fout rond de 20 %. In dit proefschrift wordt een nieuw model voor siliciumoxidatie voorgesteld, waarin elektron-gestimuleerde dissociatie van het oxiderende gas en de uitdiffusie van de gedissocieerde gassen worden meegenomen. Het is een volledig fysisch model met een beperkt aantal parameters. Dit model is in staat om de verkregen oxidatiedata te beschrijven binnen een nauwkeurigheid van 30 %. Naar verwachting kan dit verbeterd worden door de elektron-gestimuleerde dissociatie niet alleen plaats te laten vinden aan het SiO<sub>2</sub> oppervlak en aan het Si-SiO<sub>2</sub> grensvlak, maar ook binnen in het siliciumoxide.

Het inzicht dat verkregen is in de oxidatiekinetiek van silicium in een gedeutereerde omgeving is gebruikt om CMOS componenten te maken met deuterium in het gate-diëlektricum. Deuterium is ook geïntroduceerd tijdens andere processtappen. Metingen naar de kwaliteit van het binnenste van het gate-diëlektricum van deze componenten laten geen verbetering zien van de weerstand tegen degradatie. Gate-diëlektrica met deuterium degraderen even snel als gate-diëlektrica met waterstof. Dit is onafhankelijk van de processtap waarin deuterium is geïntroduceerd. Dit resultaat is acceptabel gezien de huidige kennis van SiO<sub>2</sub> degradatie, maar strookt niet met verschillende experimentele observaties in de vakliteratuur. Aan de andere kant, laten metingen naar de kwaliteit van het grensvlak van de *qate*-diëlektrica wel een verbetering van de weerstand tegen degradatie zien. Dit gebeurt echter alleen wanneer deuterium wordt geïntroduceerd tijdens de laatste processtap, de post-metal anneal. Eerdere introductie van het deuterium laat geen verbetering zien. Waarschijnlijk wordt vroegtijdig geïntroduceerde deuterium tijdens latere processtappen op hoge temperatuur vervangen door waterstof. Aangezien waterstof rijkelijk beschikbaar is tijdens het productieproces, is dit een plausibel idee.

Concluderend kan er gesteld worden dat deuterium nuttig is voor CMOS schakelingen, mits het aan het eind van het productieproces geïntroduceerd wordt, om vervanging door waterstof te voorkomen. Het enige voordeel is een hogere weerstand tegen zogenaamde hot carrier degradatie aan het grensvlak. Dit laat hogere interne elektrische velden toe in de CMOS componenten. Hot carrier degradatie is de belangrijkste reden voor de reductie van de voedingsspanning. De introductie van deuterium in het gate-diëlektricum kan de eis voor een verlaagde voedingsspanning verzachten.

### Chapter 1

### Introduction

The development of electronic integrated circuits has had and still has a large impact on society, enabling a highly automated world. Most of the electronic integrated circuits used today are Complementary MOS (CMOS) circuits, which consist mainly of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs). In the last forty years the semiconductor industry has been able to reduce the dimensions of the MOSFET tremendously. According to the International Technology Roadmap for Semiconductors [1] this reduction continues until at least 2018, enabling even faster and more complex integrated circuits. But, there are a number of hurdles on the road. One of these hurdles is the reduction of the gate dielectric thickness, the subject of this thesis.

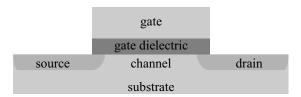

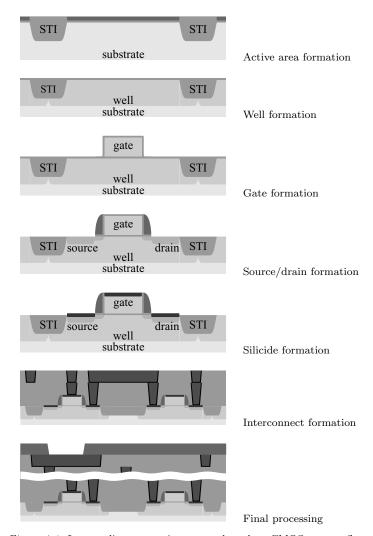

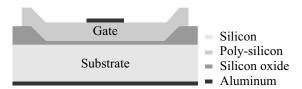

Figure 1.1 shows the basic drawing of a MOSFET. The MOSFET consists of a semiconductor (usually silicon) substrate, a source, a drain and a gate. For a n-channel MOSFET, the substrate is doped such that the majority free electric charge carriers are holes, and the source and drain are doped such that the majority free electric charge carriers are electrons. For a p-channel MOSFET the doping is reversed. The gate is electrically isolated from the substrate by the gate dielectric. When no voltage is applied to the gate, there is no electrical connection between the source and drain. When a voltage is applied to the gate (positive for a n-channel MOSFET and negative for a p-channel MOSFET), a channel of minority charge carriers will form directly underneath the gate dielectric. This channel electrically connects the source and drain. With a voltage bias applied between source and drain, an electrical current will flow. The magnitude of

the electrical current is regulated with the gate-to-substrate voltage.

Figure 1.1: Basic layout of a Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET).

In state of the art MOSFETs, the thickness of the gate dielectric is only 1 to 2 nm. The dielectric is only a few atomic layers thick. Actually, the layer has become so thin, it starts to leak electrical current and the power consumption of the electronic circuit increases. When the leakage current becomes so large that it becomes comparable to the drain current, the transistor loses its functionality. In reality, this situation is not reached, because the increase in power consumption puts severe constraints on the maximum allowable gate leakage current. Especially for mobile applications (e.g. laptop and mobile telephone) which rely on battery power, this poses a problem.

Reliability of the gate dielectric is also of concern. Under device operation conditions, the gate dielectric deteriorates, which finally results in the local breakdown of the dielectric. The dielectric has become a conductor. This strongly increases the power consumption and depending on the function of the MOSFET in the overall integrated circuit, the circuit will not function properly anymore.

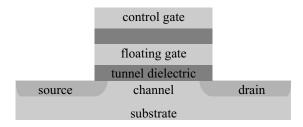

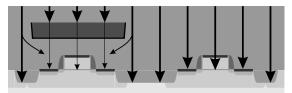

A special CMOS device extra sensitive to gate dielectric degradation is the floating gate device. It is used as a non-volatile memory device and can be found in many applications. Figure 1.2 shows the basic drawing of a floating gate device. Shown is a MOSFET with a stacked double gate. The top gate is the control gate and the bottom gate is the floating gate. The floating gate is completely electrically isolated by surrounding dielectric material. The dielectric between the floating gate and the substrate is called the tunnel dielectric. When proper voltages are applied to the control gate, source, drain and substrate, electric charge can be forced through the tunnel dielectric from the substrate to the floating gate. The reverse is also possible. The resulting charge on the floating gate represents the

stored information and can be read by sensing the drain current for a certain control gate voltage. Degradation of the tunnel dielectric implies that charge can leak away from the floating gate. This is loss of the stored information. The floating gate device does not function properly anymore.

Figure 1.2: Basic layout of a floating gate type non-volatile memory device.

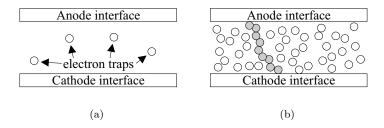

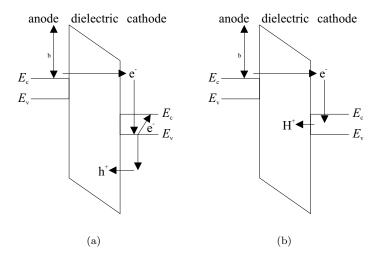

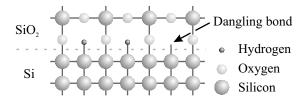

Degradation of the gate (tunnel) dielectric occurs due to the creation of defects in the dielectric and at the interface between the dielectric and the substrate. These defects are created during device operation. They are local chemical alterations, like broken chemical bonds, to the dielectric and it's interface with the substrate. There is evidence that hydrogen in CMOS devices plays a crucial role in both the creation of and passivation of defects. Hydrogen is present during many steps in the CMOS manufacturing process and is therefore abundantly available in the resulting CMOS devices.

Scanning tunnelling microscope experiments by Avouris et al. [2] showed that deuterium is harder to desorb from a silicon surface than hydrogen. This raised the idea to replace hydrogen during some stage in the CMOS manufacturing process with deuterium to improve the passivation of defects and therefore the device stability. Reports (on hot carrier degradation [3], charge-to-breakdown [4] and plasma-process induced damage [5]) indicate that the reliability of the gate dielectric in MOSFETs can be improved by introducing deuterium in the device. Improved light stability of amorphous silicon for solar cell applications [6] and improved reliability of electroluminescence [7] from MOS tunnelling diodes due to deuterium incorporation have also been reported.

Deuterium<sup>1</sup> is a hydrogen isotope. In addition to the one proton

$<sup>^{1}\</sup>mathrm{The}$  chemical notation for deuterium is  $^{2}\mathrm{H}$  or D. The last is adopted throughout this thesis.

and one electron a hydrogen atom consists of, a deuterium atom also has one neutron. Since the mass of a proton and a neutron are almost equal and much larger than the mass of an electron, a deuterium atom is twice as heavy as a hydrogen atom. This is why deuterium is sometimes called heavy hydrogen. The chemical properties of an element are controlled by the number of electrons of the element, therefore hydrogen and deuterium are chemically almost equal, but physically the factor 2 difference in mass can play a significant role. For example, the vibrational frequency of a chemical bond is proportional with the square root of the mass of the atoms involved. Consequently, a bond between a silicon atom and a hydrogen atom will vibrate at 1.4 times the frequency of a bond between a silicon atom and a deuterium atom.

The objective of this thesis is to investigate the impact of deuterium incorporation in the gate dielectric of CMOS devices on the electrical stability of these devices. The gate dielectric used throughout this thesis is silicon oxide. Deuterium can be introduced into the CMOS manufacturing process during a number of processing steps. The most direct method to incorporate deuterium into the gate dielectric is to use a deuterated method to grow the gate dielectric, i.e. to use heavy water  $(D_2O)$  or a mix of deuterium and oxygen as oxidising ambient. Little is known about the growth of silicon oxide in a deuterated ambient. To be able to grow in a deuterated ambient a silicon oxide layer with the desired thickness, a detailed knowledge of the oxidation kinetics is necessary. Therefore, chapter 2 provides a set of experimental thickness data on silicon oxidation in both a H<sub>2</sub>O and a D<sub>2</sub>O ambient for a variety of oxidation conditions. An attempt is made to model this data with existing silicon oxidation models. This modelling is not satisfactory and therefore a new silicon oxidation model is developed in chapter 3.

The growth of the gate dielectric is an early step in the process of CMOS manufacturing and many steps follow. Some of these steps introduce hydrogen. It is possible that this hydrogen replaces the deuterium introduced earlier. Chapter 4 describes a general CMOS manufacturing process and identifies the hydrogen-containing steps. The hydrogen in these steps can be replaced with deuterium. This leads to later or extra incorporation of deuterium in the CMOS manufacturing. The two extremes are formed by an early incorporation of deuterium as stated above during the gate dielectric growth and a late incorporation of deuterium during the so-called post-metal anneal.

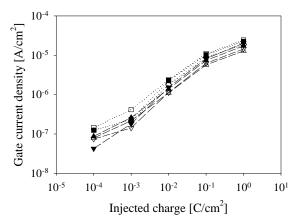

The existing literature on the impact of deuterium incorporation

on the CMOS device stability is inconsistent. The work presented in this thesis aims at resolving this inconsistency. After the description of a general CMOS manufacturing process, the specific details of the manufacturing of the devices used in this work are presented at the end of chapter 4. The electrical measurements performed at these devices are presented in chapters 5 and 6. The measurements presented in chapter 5 investigate the impact of deuterium incorporation in the CMOS manufacturing process on the bulk quality of the gate dielectric. The measurements presented in chapter 6 investigate the impact of deuterium incorporation in the CMOS manufacturing process on the quality of the interface between the substrate and the gate dielectric.

The final conclusions of the work presented in this thesis are given in chapter 7.

### Chapter 2

### Wet oxidation of silicon

#### 2.1 Introduction

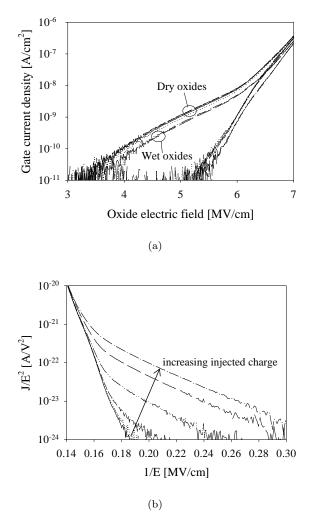

An important candidate processing step to introduce deuterium in the CMOS gate dielectric is the actual growth of the gate dielectric. This gate dielectric usually is silicon oxide, or nitrided silicon oxide. Present MOS devices demand the growth of high quality silicon oxide layers of only a few nanometres. High quality refers to low leakage current, not exceeding the Fowler-Nordheim tunnelling current, negligible fixed and mobile oxide charge and a low defect density ( $< 10^{10} \,\mathrm{cm}^{-2}$ ) at the interface with the underlying silicon. These layers have to be grown in a well controlled manner, ensuring good thickness control and uniformity. The growth is carried out in either a dry or wet ambient, where the electrical quality of wet oxides has been shown to exceed that of dry oxides [8–10]. Recent studies [4,11] indicate that replacement of hydrogen with deuterium in wet oxides, that is the use of heavy water instead of water, can further enhance the electrical quality of thin oxides. Wet oxides are also preferred in view of the lower thermal budget [12]. This is because wet oxides grow faster than dry oxides. Therefore, to assure reasonable oxidation times and good process control, thin wet oxides have to be grown at either low temperature or reduced water vapour pressure.

Little experimental oxide thickness versus oxidation time data are available on the growth of thin wet oxides. Even less data are available on the growth of thin deuterated wet oxides. In this chapter more insight and understanding into the growth of thin (1 to 60 nm) wet

and deuterated wet oxides is given. For the first time, a wide range of growth rate data of  $\rm H_2O$  and  $\rm D_2O$  oxides in an ultra-diluted ambient at different temperatures will be presented. In an attempt to gain better understanding of the oxidation process, the experimental data will be compared with various existing oxidation models.

In section 2.2 an overview of existing silicon oxidation models will be given. Three models will be treated in more detail. Section 2.3 gives the details of the experimental setup used to obtain growth data of thin wet and deuterated silicon oxides, followed by the results and discussion of the experiments in section 2.4 and the conclusions in section 2.5.

### 2.2 Existing silicon oxidation models

Silicon oxidation models are important for CMOS manufacturing. Silicon oxide is widely used during the processing and the most important step involving the growth of silicon oxide is the gate dielectric growth. The thickness of this gate dielectric is only a few nanometers and it has to be precisely controlled. For this reason a proper model of the silicon oxide thickness as a function of processing conditions is important.

There exists a broad range of models describing oxidation of silicon. In general, these models can be divided in three different groups:

- 1. Physical models, *i.e.* models derived from laws of physics, *e.g.* the Deal-Grove model [13]. These models are preferred when trying to understand the physics behind oxidation. The mathematical complexity of some physical models, *e.g.* the Beck model [14], forms a drawback for its use, especially in process simulators.

- 2. Mathematically altered physical models, *i.e.* physical models which are extended or altered in a purely mathematical manner without physical background, *e.g.* the Massoud [15] extension to the Deal-Grove model. The mathematical extension is added to overcome fitting problems of the physical model in mostly the thin oxide thickness range.

- 3. Mathematical models, *i.e.* mathematical models lacking any physical background. These models are intended to fit the available oxidation data in a quick and easy mathematical way.

In this work, the interest is in the physical understanding of thin oxide growth of silicon. Therefore, only physical models will be considered.

A good physical model will be able to describe the oxidation with a limited number of parameters, which are preferably independent of oxidation parameters like temperature and pressure and have a physical meaning, like activation energy or diffusivity. Furthermore, like any model, it should be able to describe measured data within a certain accuracy. Finally, to be of practical use, the complexity of the model should be limited. Because of this last requirement, only the Deal-Grove, the Reisman and the Wolters model will be considered. All three models have a physical basis and result in a simple mathematical relationship between oxidation time and resulting oxide thickness. Other models, like for instance the Beck model [14], result in more complex mathematical relationships.

#### Deal-Grove model

In 1965, Deal and Grove postulated a linear-parabolic growth model for silicon oxidation [13]. As a first assumption for their model, they assume that 'the oxidation proceeds by the inward movement of a species of oxidant rather than by the outward movement of silicon'. As a consequence the transported species must go through three stages:

- 1. The species is transported from the bulk of the oxidising gas to the outer silicon oxide surface.

- 2. The species is transported across the silicon oxide film towards the silicon.

- 3. The species reacts with silicon to form silicon oxide.

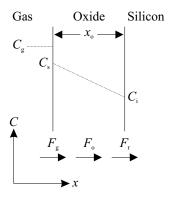

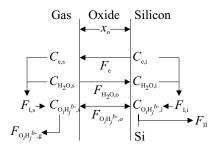

A graphical presentation of this transport is given in figure 2.1. This picture shows the concentration of the oxidising species in the oxidising gas  $(C_{\rm g})$ , at the outer surface of the silicon oxide  $(C_{\rm s})$  and at the interface between the silicon oxide and the silicon  $(C_{\rm i})$ . Furthermore it shows the flux of oxidising species from the oxidising gas to the outer surface of the silicon oxide  $(F_{\rm g})$ , the diffusion flux of oxidising species across the silicon oxide  $(F_{\rm o})$  and the flux of oxidising species corresponding to the oxidation reaction  $(F_{\rm r})$ . The silicon oxide thickness is represented by  $x_{\rm o}$ .

Figure 2.1: Concentration profile and transport of oxidising species during silicon oxidation according to the Deal-Grove model. This picture shows the concentration of the oxidising species in the oxidising gas  $(C_g)$ , at the outer surface of the silicon oxide  $(C_s)$  and at the interface between the silicon oxide and the silicon  $(C_i)$ . Furthermore it shows the flux of oxidising species from the oxidising gas to the outer surface of the silicon oxide  $(F_g)$ , the diffusion flux of oxidising species across the silicon oxide  $(F_o)$  and the flux of oxidising species corresponding to the oxidation reaction  $(F_r)$ . The silicon oxide thickness is represented by  $x_o$ .

The three fluxes are described by:

$$F_{g} = h(C_{g} - C_{s}) \tag{2.1}$$

$$F_{\rm o} = D_{\rm eff} \frac{\partial C}{\partial x} = D_{\rm eff} \left( \frac{C_{\rm s} - C_{\rm i}}{x_{\rm o}} \right)$$

(2.2)

$$F_{\rm r} = kC_{\rm i} \tag{2.3}$$

$$F_{\rm g} = F_{\rm o} = F_{\rm r} = F \tag{2.4}$$

In these equations, h,  $D_{\rm eff}$  and k are a gas-phase transport coefficient, the effective diffusion coefficient for the oxidising species in silicon oxide and the reaction rate constant for the formation of silicon oxide from the oxidising species and silicon. The second assumption of Deal and Grove is that of steady-state conditions, that is there is no accumulation or depletion of oxidising species or equivalently the flux of oxidising species is independent of position. This is implemented in equation 2.2 in the rightmost term and by the equality of the three fluxes described in equation 2.4.

Solving equations 2.1 to 2.4 results in:

$$F = \frac{kC_{\rm g}}{1 + \frac{k}{h} + \frac{kx_{\rm o}}{D_{\rm off}}} \tag{2.5}$$

With N the number of oxidant molecules incorporated in a unit volume of the silicon oxide layer, the growth rate can be expressed as:

$$\frac{dx_{\rm o}}{dt} = \frac{F}{N} = \frac{kC_{\rm g}}{N\left(1 + \frac{k}{h} + \frac{kx_{\rm o}}{D_{\rm eff}}\right)}$$

(2.6)

Deal and Grove integrate this equation starting from an initial silicon oxide thickness  $x_i$  stating that this initial silicon oxide layer can be regarded as the thickness of the layer grown before the above assumptions become valid. The result is:

$$\frac{x_{\rm o}^2}{B} + \frac{x_{\rm o}}{B/A} = (t+\tau)$$

(2.7)

with

$$B/A = \frac{C_{\rm g}}{N\left(\frac{1}{h} + \frac{1}{k}\right)} \tag{2.8}$$

$$B = \frac{2D_{\text{eff}}C_{\text{g}}}{N} \tag{2.9}$$

and

$$\tau = \frac{x_{\rm i}^2}{B} + \frac{x_{\rm i}}{B/A} \tag{2.10}$$

The parameters B/A and B are the linear and parabolic rate constants. The linear rate constant is determined by the interface reaction constant, while the parabolic rate constant depends on both the interface reaction constant and the diffusion constant of the oxidation species in silicon oxide. The constant  $\tau$  gives the time needed to grow an initially present oxide thickness  $x_i$ . Since temperature dependence of the diffusion and reaction rate constants can be described with Arrhenius equations, the temperature dependence of the linear and parabolic rate constants can also be described with Arrhenius equations. The pressure dependence of the rate constants is linear as this is determined by the concentration of the oxidising species in the oxidising gas.

The Deal-Grove model is a simple and complete model. Moreover, it is able to describe a large portion of the existing silicon oxidation data. Therefore, it is widely applied. However, it is known to be unsuccessful in explaining the growth of thin (0 to 20 nm) oxides in dry oxygen [16], namely oxidation occurs faster than the model predicts.

#### Reisman model

The Deal-Grove model cannot describe the growth of thin (0 to  $20 \,\mathrm{nm}$ ) oxides in dry oxygen. This is why Reisman *et al.* [17] propose a different silicon oxidation model. They show that a wide variety of dry oxidation data can be modelled with a simple power law. They used data from several sources, for both <100> and <111> silicon within a oxidation temperature range of 700 to  $1000\,^{\circ}\mathrm{C}$  and a oxidation pressure range of  $1\times10^{-5}$  to  $20 \,\mathrm{atm}$ . Later Nicollian and Reisman [18] provided a physical basis for the observed power law.

On the basis of the values of the fitting constants found in [17], Reisman and Nicollian argue that the silicon oxide forming reaction is the rate-limiting step at all times. This is in contrast with the Deal-Grove model which also considers the diffusion of the oxidising species to be a rate-limiting step. The key point in the Reisman model is the assumption that the surface reaction is retarded by the viscous flow of the silicon oxide to accommodate the volume expansion that occurs when silicon oxidises. They state that 'oxidation cannot proceed unless free volume is provided to accommodate the newly forming oxide which occupies approximately 2.2 times the volume of the silicon from which it is formed'.

The above considerations lead to the following description of the growth rate:

$$\frac{dx_{\rm o}}{dt} = k_{\rm v}(t, p, T)C_{\rm os}^n \tag{2.11}$$

In this equation,  $C_{os}$  is the concentration of the oxidising species at the reaction surface and n is the partial order of the surface reaction. Due to the assumption that diffusion of the oxidising species is not a rate-limiting step,  $C_{os}$  is determined solely by the partial pressure of the oxidising species in the oxidising gas.

The reaction rate constant  $k_{\rm v}$  depends on oxidation time, pressure and temperature, since it is controlled by the silicon oxide viscosity. In

general, the reaction rate constant can be described by an Arrhenius equation:

$$k_{\rm v}(t, p, T) = k_{\rm A} e^{-\frac{[E_{\rm v}(t, p, T) + E_{\rm r}]}{kT}}$$

(2.12)

The activation energy consists of two parts. The first part is the oxidation time, pressure and temperature dependent energy  $E_{\rm v}$  required to produce the free volume by viscous flow to accommodate the volume expansion. The second part,  $E_{\rm r}$  is 'the remaining energy required for the reaction. The latter includes the activation energy required to break Si–Si bonds, for example.'

At the same time, the energy  $E_{\rm v}$  also represents the activation energy of the average viscosity of the silicon oxide:

$$\eta(t, p, T) = \eta_o e^{-\frac{E_v(t, p, T)}{kT}}$$

(2.13)

The crux of the physical basis of the Reisman model lies in a proper time dependent description of the average viscosity of the silicon oxide. To arrive at the desired power law for the silicon oxide growth, and in line with other people describing the time dependence of glass viscosity [19], Nicollian and Reisman use a power law to describe the time dependence of the average viscosity:

$$\eta(t, p, T) = G(t - \tau)^{\phi(p, T)}$$

(2.14)

In this equation, G is a constant,  $\tau$  represents an incubation time for initial oxidation and  $\phi$  determines the shape of the  $\eta$ -t curve.

Combining equations 2.11 to 2.14 results in:

$$\frac{dx_{\rm o}}{dt} = \frac{k_{\rm A}\eta_{\rm o}C_{\rm os}^n}{G\left(t+\tau\right)^{\phi(p,T)}}e^{-\frac{E_{\rm r}}{kT}} \tag{2.15}$$

Integrating this equation starting at an initial oxide thickness leads to the desired power law:

$$x_{o} = a \left( t + \tau \right)^{b} \tag{2.16}$$

with

$$b = 1 - \phi(p, T) \tag{2.17}$$

$$a = \frac{k_{\rm A} \eta_{\rm o} C_{\rm os}^n}{Gb} e^{-\frac{E_{\rm r}}{kT}} \tag{2.18}$$

and

$$\tau = \sqrt[b]{\frac{x_{\rm i}}{a}} \tag{2.19}$$

The oxidation temperature and pressure dependence of the model parameters a and b is more complicated than in the case of the Deal-Grove model. A specific temperature and pressure dependence for  $\phi(p,T)$  is not available and probably quite complicated. The only simple temperature and pressure dependence that can be derived is that for the product ab. The pressure dependence of this product is determined by  $C_{\rm os}$ . Therefore, the product is similar to the nth power of the pressure. The temperature dependence is described by the Arrhenius term with an activation energy of  $E_{\rm r}$ .

The Reisman model is a rather sophisticated model and not complete. The temperature and pressure dependence of the direct model parameters is as stated in the former paragraph not known. It is capable of describing a wide variety of oxidation data [17].

#### Wolters model

The last physical model considered, is the model by Wolters and Zegers-van Duijnhoven [20]. Wolters and Zegers-van Duijnhoven have three reasons to propose a different silicon oxidation model: The Deal-Grove model cannot describe the growth of thin oxides in dry oxygen, since silicon oxidation occurs even at room temperature the silicon oxide forming reaction cannot be a rate-limiting step, and the work of Jorgensen [21] shows that the application of an external electric field influences the oxidation rate of silicon and can even completely stop oxidation. The last reason is why Wolters and Zegers-van Duijnhoven consider the oxidation of silicon to occur due to ionic transport. A mechanism which is also used to describe the oxidation of metals.

The derivation of the Wolters model is done for the case of silicon oxidation in an oxygen ambient, but it is also applicable to the case of wet oxidation. The model assumes an electron flow from the Si-SiO<sub>2</sub> interface into the growing silicon oxide, reacting with oxygen diffusing into the oxide from the ambient to form oxygen ions:  $O_2 + 2ze^- \longrightarrow 2O^{z-}$ . This reaction is assumed to be in a local equilibrium throughout the oxide. Taking this into account as well as the requirement that there is no net electrical current, the model arrives

at:

$$J_{\mathcal{O}^{z-}} = -\frac{\left(\sigma_{\mathbf{e}}^{-1} + \sigma_{\mathrm{ion}}^{-1}\right)^{-1}}{2z^{2}q^{2}} \frac{d\mu_{\mathcal{O}_{2}}}{dx}$$

(2.20)

In this equation,  $J_{\mathrm{O^2}^-}$  represents the flow of oxygen ions,  $\sigma_{\mathrm{e}}$  and  $\sigma_{\mathrm{ion}}$  the conductivity of electrons and oxygen ions in the growing silicon oxide and  $\mu_{\mathrm{O_2}}$  the oxygen thermodynamical potential. When assuming that the conductivities  $\sigma_{\mathrm{e}}$  and  $\sigma_{\mathrm{ion}}$  are independent of the position in the silicon oxide, equation 2.20 will result in the classical parabolic ionic-transport model developed by Wagner [22]. However, it is known that a parabolic model is not sufficient to describe silicon oxidation. The Wolters model assumes the oxygen ions to migrate through the silicon oxide layer by jumping from one potential well to another, resulting in a field-dependent ion conductivity:

$$\sigma_{\rm ion} = \sigma_{\rm o} e^{\left(-\frac{zqaE}{kT}\right)} \tag{2.21}$$

In this equation a represents half the hopping distance and  $\sigma_0$  the ion conductivity at zero electric field.

According to equation 2.21, the ion conductivity decreases exponentially with increasing electric field. A local higher electric field will decrease the ionic transport. According to the Wolters model, to sustain the necessary ion flow  $J_{\mathrm{O^{z-}}}$ , the local electric field has to increase. This is a self-supporting effect with as a result that most of the thermodynamic potential difference stands over a thin layer of silicon oxide at the  $\mathrm{Si\text{-}SiO_2}$  interface with low ion conductivity. The ion conductivity in the remaining silicon oxide layer is high. Taking the series connection of these two conductivity regions into account in equation 2.20 the Wolters model arrives after a few approximations at a power-parabolic law:

$$x_{\rm o}^2 + Ax_{\rm o}^{2-\alpha} = Bt (2.22)$$

with

$$\alpha = \frac{a\left(\sigma_{\rm e}^{-1} + \sigma_{\rm ion}^{-1}\right)^{-1}}{kT} \frac{\Delta\mu_{\rm O_2}}{x_{\rm Q}}$$

(2.23)

$$A = \frac{2}{2 - \alpha} e^{\alpha} x_{\mathcal{Q}}^{\alpha} \frac{\sigma_{\mathbf{e}}}{\sigma_{\mathcal{Q}} + \sigma_{\mathbf{e}}}$$

(2.24)

and

$$B = \frac{\left(\sigma_{\rm e}^{-1} + \sigma_{\rm ion}^{-1}\right)^{-1} \Delta \mu_{\rm O_2}}{Nz^2 q^2}$$

(2.25)

With N the number of oxidant molecules incorporated in a unit volume of the silicon oxide layer and  $x_Q$ , the thickness of the low ion conductivity layer. The model reduces to a linear-parabolic law in case  $\alpha=1$  and to a power law in case  $A\gg x^{\alpha}$ . The first has the same thickness-time relation as the Deal-Grove model and the latter as the Reisman model. As with the Reisman model, there is no clear relation between the model parameters  $\alpha$ , A and B and the oxidation temperature and pressure.

### 2.3 Experimental setup

A wide range of oxidation experiments in ultra-diluted wet ambient were carried out to investigate the silicon oxide growth rate. The experiments were conducted using 100 mm p-type wafers with a <100> orientation and a boron doping concentration of  $6\times10^{14}$  cm<sup>-3</sup>. Prior to oxidation the wafers were cleaned and dipped in a 1% HF solution until the wafer surface was hydrophobic. Directly following the final rinse, the wafers were loaded into the oxidation furnace.

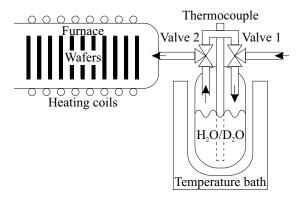

The oxidation was performed in a horizontal furnace. Depending on the valve settings, dry nitrogen flowed either directly or via a small tank into the furnace, see figure 2.2. The nitrogen flow rate was set at 41/min. The small tank contained either  $H_2O$  or  $D_2O$  allowing the nitrogen to take up (heavy) water vapour. The temperature of the tank, which is the minimum temperature in the system, determined the water vapour pressure of the outcoming wet nitrogen gas. For  $H_2O$  the tank temperature was set at 17.5 °C and for  $D_2O$  at 20 °C. These temperatures correspond to a saturated vapour pressure of 0.020 atm for both species [23].

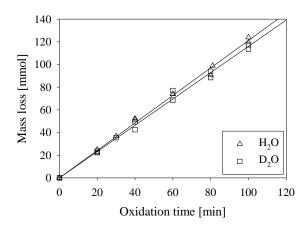

The actual vapour pressure of the outcoming nitrogen gas was estimated by measuring the mass loss of the tank during the oxidation. The measured mass loss is plotted versus oxidation time in figure 2.3. The slope of the linear regression lines is  $1.21 \pm 0.01 \, \text{mmol/min}$  for  $\text{H}_2\text{O}$  and  $1.16 \pm 0.01 \, \text{mmol/min}$  for  $\text{D}_2\text{O}$ . There is a difference of 4%. Taking into account the nitrogen flow of  $4 \, \text{l/min}$ , the precursor partial pressure is calculated to be  $7 \times 10^{-3} \, \text{atm}$ .

The wafers were loaded at a temperature of 700 °C under dry nitrogen flow. Nonetheless, during loading, clean room air is transported into the furnace along with the wafers. To minimise the effect of this clean room air, the furnace temperature was maintained for five minutes at maximum nitrogen flow. Then, the temperature was

Figure 2.2: The oxidation system. During standby, loading, temperature ramp up and down and unloading, the valve settings are such that dry nitrogen flows directly into the furnace. During oxidation the valves are switched to lead dry nitrogen through the small tank taking up  $\rm H_2O$  or  $\rm D_2O$  vapour before entering the furnace. The temperature of the small tank and therefore the saturated vapour pressure of the (heavy) water is controlled with a temperature bath and thermocouple. The temperature of the furnace is controlled with heating coils.

Figure 2.3: Amount of oxidising species introduced into the furnace as a function of oxidation time.

ramped up to the oxidation temperature with 10 °C/min. Oxidation time and temperature were varied from 0 to 960 min and from 750 to 950 °C. After the oxidation temperature was reached, the nitrogen was passed through the tank allowing it to take up (heavy) water

vapour. After oxidation, the temperature was ramped down under dry nitrogen flow to 700 °C with 2.5 °C/min, before the wafers were unloaded.

The resulting oxide thickness was measured at 80 points across the wafer and averaged. The edge exclusion was set to 5 mm. The measurements were carried out with a PLASMOS ellipsometer using a He:Ne laser ( $\lambda = 632.8 \, \mathrm{nm}$ ) at an incident angle of 70°. The refractive index was fixed at 1.456.

The measured oxidation data were compared with existing oxidation models by fitting the models with a least squares fit minimising the relative error between the data and the model.

### 2.4 Results and discussion

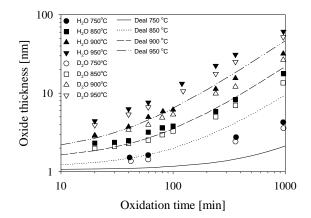

Oxide thickness was measured as a function of oxidation time and temperature. The measurements across the wafers showed that the thickness non-uniformity of the grown oxide layers was less than 5%. The measured oxide thickness is plotted versus time in figure 2.4. The values are listed in table 2.1. Figure 2.4 indicates that, for the same oxidation time and temperature, the oxide grown in  $H_2O$  ambient is considerable thicker than the oxide grown in  $D_2O$  ambient.

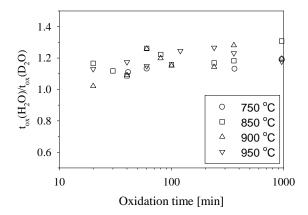

The distance between the curves on the log-log scale appears to be constant which implies a constant ratio between the oxide thickness grown in  $\rm H_2O$  and  $\rm D_2O$  ambient independent of time and temperature. This observation is confirmed in figure 2.5. For the investigated oxidation pressure the ratio is:

$$\frac{x_{\rm H_2O}(t,T)}{x_{\rm D_2O}(t,T)} = 1.18 \pm 0.07 \tag{2.26}$$

The difference of 18% in oxide growth could be due to either the measured difference in water partial pressure, or the different oxidation ambient. However, it follows from [16] that typically the pressure dependence of oxide growth is described by a power law:

$$x \sim p^n \tag{2.27}$$

with  $0.5 \le n \le 1.0$ . This implies that the 4% difference in  $\rm H_2O/D_2O$  partial pressure will at most result in 4% difference in oxidation rate. The difference in oxidation pressure cannot completely explain the measured 18% difference in oxidation rate. Therefore, the difference

Figure 2.4: Silicon oxide thickness (measured by ellipsometer) as a function of oxidation time for oxidation in a  $\rm H_2O$  and  $\rm D_2O$  ambient (partial pressure is  $7\times 10^{-3}$  atm) in the temperature range of 750 to 950 °C. The markers indicate the measured data, while the lines indicate the prediction of the Deal-Grove model for a  $\rm H_2O$  ambient using the parameter values extracted by Deal [24]. These values are listed in table 2.2.

Table 2.1: Measured silicon oxide thickness (in nm) for oxidation in a  $\rm H_2O$  and  $\rm D_2O$  ambient (partial pressure is  $7\times 10^{-3}$  atm) for an oxidation time of 0 to 960 min and an oxidation temperature of 750 to 950 °C.

| Time  | 750 °C     |        | 850 °C     |        | 900 °C       |        | 950 °C     |                 |

|-------|------------|--------|------------|--------|--------------|--------|------------|-----------------|

| (min) | $\rm H_2O$ | $D_2O$ | $\rm H_2O$ | $D_2O$ | ${\rm H_2O}$ | $D_2O$ | $\rm H_2O$ | $\mathrm{D_2O}$ |

| 0     | 1.06       | 1.06   | 1.14       | 1.14   | 1.43         | 1.43   | 1.71       | 1.71            |

| 20    | -          | -      | 2.31       | 1.98   | 2.90         | 2.84   | 4.41       | 3.90            |

| 30    | -          | -      | 2.36       | 2.11   | -            | -      | -          | -               |

| 40    | 1.51       | 1.36   | 2.49       | 2.29   | 3.73         | 3.42   | 6.28       | 5.35            |

| 60    | 1.62       | 1.43   | 3.18       | 2.52   | 4.96         | 3.94   | 7.61       | 6.62            |

| 80    | -          | -      | 3.62       | 2.96   | 5.85         | 4.88   | -          | -               |

| 100   | -          | -      | 3.81       | 3.29   | 6.15         | 5.34   | -          | -               |

| 120   | -          | -      | -          | -      | -            | -      | 13.24      | 10.63           |

| 240   | -          | -      | 5.86       | 5.01   | 11.31        | 9.89   | 22.44      | 17.71           |

| 360   | 2.74       | 2.42   | 8.27       | 6.99   | 15.52        | 12.11  | 30.96      | 25.14           |

| 960   | 4.26       | 3.57   | 17.73      | 13.55  | 31.87        | 26.65  | 60.99      | 51.77           |

in oxidation rate must largely be attributed to an isotope effect. For example, a difference of 15 to 17 meV in activation energy suffices to give a change of 18 % in oxidation rate in the temperature range of 750 to 950 °C.

Figure 2.5: Oxide thickness for  $\rm H_2O$  oxidation divided by oxide thickness for  $\rm D_2O$  oxidation as a function of oxidation time in the temperature range of 750 to 950 °C.

Table 2.1 also lists the oxide thickness for zero oxidation time. This is the oxide grown in clean room ambient at room temperature, during loading, temperature ramp-up, temperature ramp-down and unloading, without actual oxidation in  $H_2O$  or  $D_2O$  ambient. This oxide has to be attributed mainly to clean room ambient coming into the furnace during loading and is taken to be the initial oxide thickness  $x_i$  for actual oxidation as intended in this experiment.

The measured oxidation data were first compared with the Deal-Grove model. Deal [24] measured the model parameters B and B/A for pyrogenic  $H_2O$  oxidation at a partial pressure of 640 torr. These values are commonly used [16]. There are no known values for oxidation in a  $D_2O$  ambient. Table 2.2 lists the parameter values measured by Deal for a partial pressure of 0.84 atm (640 torr) and the extrapolated values for  $7 \times 10^{-3}$  atm, using the linear pressure dependence of the parameters. The oxidation curves predicted by using these values for  $H_2O$  oxidation are depicted in figure 2.4 by the lines. The initial oxide thickness  $x_i$  is set equal to the measured oxide thickness for zero oxidation time as listed in table 2.1. Comparison of the Deal-Grove model with the  $H_2O$  oxidation data shows that the Deal-Grove model consequently underestimates the oxide thickness in the investigated range by 15 to 40 %.

Table 2.2 also lists fitted parameters for both  $H_2O$  and  $D_2O$  oxidation. These parameters are obtained by minimising the relative square deviation between model and data. The fitted values for the

Table 2.2: Deal-Grove model parameter values for a partial pressure of 0.84 atm (640 torr) as measured by Deal [24] and extrapolated to  $7 \times 10^{-3}$  atm. Also given are the fitted parameter values and fitted initial oxide thickness,  $x_i$ , for a relative least square error fit of the measured oxidation data.

|                                                                                                 | B/A                                                                                 |                                      | В                                      | $x_i$                        |                          |                              |                              |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|------------------------------|--------------------------|------------------------------|------------------------------|

|                                                                                                 | $\frac{C}{(\mu \text{m/hr})}$                                                       | $E_a$ (eV)                           | $\frac{C}{(\mu \text{m}^2/\text{hr})}$ | $E_a$ (eV)                   | T (°C)                   | (n:<br>H <sub>2</sub> O      | m)<br>D <sub>2</sub> O       |

| $0.84\mathrm{atm}$ $7\times10^{-3}\mathrm{atm}$ fit for $\mathrm{H_2O}$ fit for $\mathrm{D_2O}$ | $9.70 \times 10^{7}$ $8.07 \times 10^{5}$ $2.28 \times 10^{6}$ $1.73 \times 10^{6}$ | 2.05<br>2.05<br>2.05<br>2.05<br>2.05 | 386<br>3.21<br>0.624<br>0.463          | 0.78<br>0.78<br>0.82<br>0.82 | 750<br>850<br>900<br>950 | 1.26<br>1.40<br>1.50<br>1.77 | 1.16<br>1.29<br>1.50<br>1.75 |

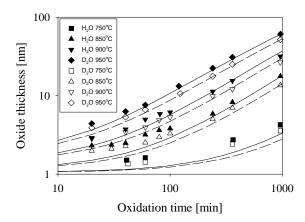

activation energies are equal or close to the values obtained by Deal, but the pre-exponential factors are deviating strongly. The classical Deal-Grove model clearly fails. Figure 2.6 compares the Deal-Grove model using the fitted parameters to the measured data from table 2.1. The deviation between the model and the data is large for both short and long oxidation times. The relative error between fitted model and measured data still is in the range of 20%. It can be concluded that, though simple and applicable to a wide range of data, the Deal-Grove model does not fit the measured data for a wet ultra-diluted ambient in a satisfactory manner.

Figure 2.6: Comparison of the measured data from table 2.1 and the Deal-Grove model using the fitted parameter values listed in table 2.2. The solid lines are the fitted curves for  $\rm H_2O$  and the dashed lines are the fitted curves for  $\rm D_2O$ .

Table 2.3: Reisman a parameter values and fitted initial oxide thickness,  $x_i$ , which best fits the measured oxidation data of table 2.1. The best fitting activation energy and pre-exponential factor for the product ab are  $0.40\,\mathrm{eV}$  and  $8.87\,\mathrm{nm/min}^b$  for  $\mathrm{H_2O}$  and  $0.42\,\mathrm{eV}$  and  $8.96\,\mathrm{nm/min}^b$  for  $\mathrm{D_2O}$  respectively.

| T<br>(°C) |              | $\min^b$                 | (n         | m)     |

|-----------|--------------|--------------------------|------------|--------|

|           | ${\rm H_2O}$ | $\mathrm{D}_2\mathrm{O}$ | $\rm H_2O$ | $D_2O$ |

| 750       | 0.232        | 0.176                    | 1.08       | 1.07   |

| 850       | 0.243        | 0.195                    | 1.17       | 1.17   |

| 900       | 0.248        | 0.201                    | 1.42       | 1.46   |

| 950       | 0.251        | 0.207                    | 1.76       | 1.77   |

The second model that is compared with the oxidation data is the Reisman model. For this model no known values are available for silicon oxidation in either a  $H_2O$  or  $D_2O$  ambient. Secondly, the model only provides an explicit temperature dependence for the product of the parameters a and b. This implies that for every temperature, a has to be fitted separately and b follows from a and the Arrhenius pre-exponential factor and activation energy of the product ab.

The fitted parameter values for the Reisman model are listed in table 2.3. The relative error between the Reisman model using these parameter values and the measured data is plotted in figure 2.7. This figure also shows the relative error for the Deal-Grove model. The error is on average less for the Reisman model, but the maximum error still is  $15\,\%$ . Furthermore, the fact that there is no explicit temperature dependence for a forms a drawback for using this model. Therefore, although the fit for the Reisman model is slightly better, there is no benefit in using this model instead of the Deal-Grove model.

The last model that is compared with the measured oxidation data is the Wolters model. This model does not supply an obvious temperature dependence for its parameters. Therefore, the three model parameters  $\alpha$ , A and B have to be fitted separately for every temperature. This accumulates to the matrix of parameters listed in table 2.4. As with the Reisman model there are no known values in literature to be compared to. The fact that none of the parameters have an explicit temperature dependence forms a severe drawback for using this model. Furthermore, as can be seen in figure 2.7 the relative error between the fitted Wolters model and the measured data is almost identical to the relative error obtained for the Reisman

Figure 2.7: Relative error between the measured data from table 2.1 and the three oxidation models considered in this chapter as a function of oxide thickness. The parameters values used in the models are listed in tables 2.2, 2.3 and 2.4.

Table 2.4: Wolters model parameter values which best fits the measured oxidation data of table 2.1.

| T<br>(°C) | α<br>(-)              |                       | $a \pmod{\operatorname{nm}^{\alpha}}$ |        | (nm <sup>2</sup> | b<br>/min)      | $x_{i}$ (nm)            |        |

|-----------|-----------------------|-----------------------|---------------------------------------|--------|------------------|-----------------|-------------------------|--------|

|           | $\mathrm{H_{2}O}$     | $\mathrm{D_2O}$       | $\rm H_2O$                            | $D_2O$ | $\rm H_2O$       | $\mathrm{D_2O}$ | $\overline{{\rm H_2O}}$ | $D_2O$ |

| 750       | $5.31 \times 10^{-4}$ | $6.56 \times 10^{-4}$ | 2.15                                  | 2.03   | 0.0579           | 0.0384          | 1.12                    | 1.10   |

| 850       | 0.561                 | 0.660                 | 7.29                                  | 5.78   | 0.601            | 0.324           | 1.20                    | 1.20   |

| 900       | 0.758                 | 0.730                 | 30.2                                  | 25.8   | 3.06             | 2.16            | 1.46                    | 1.48   |

| 950       | 0.870                 | 0.806                 | 63.9                                  | 85.1   | 10.5             | 12.0            | 1.73                    | 1.74   |

model. Taking into account the lack of a proper description of the temperature dependence of the model, the Deal-Grove model is still preferred, although the parameters values needed for the best possible fit are deviating strongly from the values obtained by Deal [24].

### 2.5 Conclusions

Oxidation data, *i.e.* oxide thickness as a function of oxidation time, has been obtained for silicon oxidation in ultra-diluted (partial pressure  $0.7\,\mathrm{kPa}$ )  $\mathrm{H_2O}$  and  $\mathrm{D_2O}$  ambient at different temperatures. The oxidation data shows that the silicon oxidation rate in a  $\mathrm{D_2O}$  ambient

is 18 % lower than in a  $\rm H_2O$  ambient. This is independent of oxidation time and thickness. A difference of 15 to 17 meV in activation energy suffices to give a change of 18 % in oxidation rate in the investigated temperature range of 750 to 950 °C.

An attempt to model the obtained oxidation data with existing physical oxidation models is not satisfactory. The Deal-Grove, Reisman and Wolters model are equally good in describing the data. Since the Reisman and Wolters model do not specify how the model parameters depend on oxidation temperature and pressure, the Deal-Grove model is preferred. However, the parameter values needed to fit the Deal-Grove model to the obtained data are not in accordance with values reported in literature and the relative error still remains in the range of  $20\,\%$ .

# Chapter 3

# New oxidation model

### 3.1 Introduction

In the former chapter, oxidation data, *i.e.* oxide thickness as a function of oxidation time, has been obtained for silicon oxidation in ultradiluted  $\rm H_2O$  and  $\rm D_2O$  ambient at different temperatures. An attempt to model the obtained oxidation data with existing physical oxidation models is not satisfactory. This raises the need for a new oxidation model. As already stated in section 2.2 a proper silicon oxidation model is necessary to be able to predict the obtained silicon oxide thickness for a certain set of processing conditions. Especially for the gate dielectric a good control of the oxide thickness is essential. Furthermore, a sound physical model can give more understanding in the silicon oxidation process. This better understanding might be linked to the quality of a silicon oxide layer for a certain set of processing conditions.

In this chapter a new silicon oxidation model is proposed to explain the data obtained in the former chapter. Before postulating the new silicon oxidation model, section 3.2 takes a closer look at the initial oxidation regime of silicon. Based on this, the new oxidation model incorporates a tunnelling regime. The concept of electron tunnelling will first be introduced in section 3.3 and will be followed by the postulation of the new silicon oxidation model in section 3.4. In section 3.5, the new oxidation model will be verified on the oxidation data obtained in the former chapter. Finally, conclusions will be drawn in section 3.6.

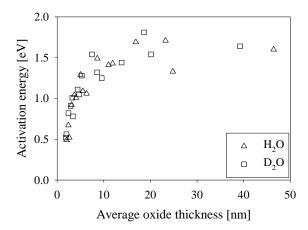

Figure 3.1: Activation energy extracted from the measured oxidation data in table 2.1 as a function of average oxide thickness for  $\rm H_2O$  and  $\rm D_2O$  ambient. The activation energy is extracted from every pair of adjacent measurement points for the same oxidation time, but different oxidation temperatures.

## 3.2 Initial oxidation regime

The three models discussed in chapter 2 are not completely satisfactory in explaining the measured data in a solid physical way. While a solid physical use of the Deal-Grove model results in a poor fit, the other two models fit just slightly better and do not relate one or more parameters to temperature, resulting in a separate set of parameters for every temperature.

To obtain further insight in the oxidation process, the activation energy for the oxide thickness is calculated for different thicknesses. The result is shown in figure 3.1. Two observations can be made from this graph. Firstly, the activation energy for  $\rm H_2O$  and  $\rm D_2O$  grown oxides is similar. Secondly, the activation energy is changing going from ultra-thin oxides to thin oxides. This indicates a change in oxidation mechanism. However, a reservation has to be made.

The initial oxide thickness  $x_i$  influences the measured oxide thickness as a function of time. If the initial oxide had not been present before the actual oxidation process had started, the final oxide would have been thinner. For thick oxides, the influence is small, but for thin oxides, the influence can be substantial. This implies that the activation energy for ultra-thin oxides will be higher than presented

Figure 3.2: Electron tunnelling through an energy barrier.

in figure 3.1.

The trend of a lower activation energy for ultra-thin oxides can be expected, considering the fact that a thin native oxide layer forms on a bare silicon wafer even at room temperature. The growth of this native oxide practically stops when a certain layer thickness is reached. The examined models do not predict this fast initial oxidation at room temperature. A new model extension is necessary to describe the oxide growth in the regime below 10 nm.

The initial oxidation rate is high, but slows down abruptly after a few nanometres. The initial oxidation regime is also relatively weakly temperature dependent because a native oxide will already form at room temperature. This native oxide grows rapidly, but is limited to 1 to 2 nm. After this thickness, the oxidation rate at room temperature is so low that the oxidation practically stops. A viable candidate to explain this initial oxidation behaviour of silicon is a tunnelling-stimulated process. Electron tunnelling is only weakly dependent on temperature and the electron tunnelling probability depends exponentially on the oxide thickness. This can explain the transition from fast to slow oxidation.

## 3.3 Electron tunnelling

Figure 3.2 shows an electron encountering an energy barrier. In classical mechanics the electron with an energy  $\phi_b$  below the energy barrier is totally reflected by the barrier. However, in quantum mechanics the electron can be described by a probability wave. This probability wave will also be reflected by the barrier, but a small evanescent probability field will exist inside the barrier. When the barrier is thin enough, the evanescent probability field will be non-zero at the other side and the electron has a certain possibility of turning up at the other side of the barrier. This is called tunnelling. The tunnelling probability of an electron in case of a square barrier can be approxi-

mated by [25]:

$$P = e^{\frac{-2x_{\rm o}\sqrt{2m_{\rm e}\phi_{\rm b}}}{\hbar}} \tag{3.1}$$

with  $x_0$  the thickness of the barrier,  $m_e$  the effective electron mass inside the barrier,  $\phi_b$  the barrier height and hbar the reduced Planck constant.

In case of a silicon substrate covered by a thin layer of silicon oxide, the energy of the tunnelling electron can be the bottom of the conduction band and the barrier is formed by the large forbidden band gap of the silicon oxide. The energy level where the electron will tunnel to can be an energy level of an adsorbed molecule at the silicon oxide surface. At practical oxidation temperatures, the concentration of electrons in the silicon, will equal the intrinsic electron concentration  $C_{\rm e,i}$ . Due to the tunnel probability of the electrons through the barrier, adsorbed molecules will see a virtual concentration of electrons at the ambient side of the barrier equal to:

$$C_{\rm e,s} = C_{\rm e,i} P = C_{\rm e,i} e^{\frac{-2x_{\rm o}\sqrt{2m_{\rm e}\phi_{\rm b}}}{\hbar}}$$

(3.2)

This is the concentration of electrons available for reaction at the surface of the silicon oxide.

### 3.4 New oxidation mechanism

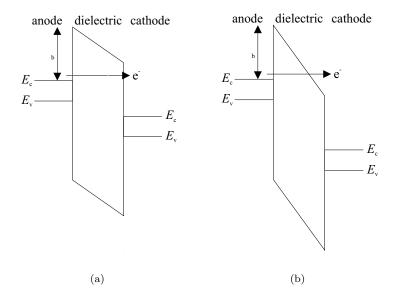

In an attempt to overcome the problems of the models used in the former chapter, a new oxidation model is proposed. A viable candidate for describing the rapid initial oxidation is electron-stimulated dissociation. Electron tunnelling heavily depends on the silicon oxide thickness, while it hardly depends upon temperature. This electron tunnelling will be embedded in a modified Deal-Grove model.

To accommodate for the electron-stimulated dissociation, it is postulated that the reaction between the oxidising species and the silicon proceeds in two steps. Step I is the electron-stimulated dissociation of the oxidising species, and step II is the formation of silicon oxide from the reaction product  $O_iH_i^{b-}$  and silicon. In chemical formula:

**Reaction II**

$$d O_i H_i^{b-} + m \operatorname{Si} \xrightarrow{k_{\text{II}}} g \operatorname{SiO}_2 + n \operatorname{H}_2 + b \operatorname{e}^{-}$$

Figure 3.3: Transport of the different species according to the new oxidation mechanism.

The product of reaction I  $(O_iH_j^{b-})$  is a species consisting of oxygen and possible hydrogen. The key-point in this model is the fact that the overall reaction is split in two and stimulated by electrons.

Reaction II takes place at the Si-SiO<sub>2</sub> interface. Reaction I can take place both at the Si-SiO<sub>2</sub> interface and at the silicon oxide surface. At the interface electrons are freely available in the silicon, while at the surface, the electrons have to be supplied by tunnelling. An overall picture of the reactions and fluxes of species is given in figure 3.3. In this figure  $F_{I,s}$  and  $F_{I,i}$  are the fluxes associated with reaction I at respectively the silicon oxide surface and the Si-SiO<sub>2</sub> interface,  $F_{\rm II}$  is the flux associated with reaction II at the interface,  $F_{\rm O_i H_j^{b^-},o},\,F_{\rm O_i H_j^{b^-},g},\,F_{\rm H_2O,o}$  are fluxes due to the diffusion of the reaction product in the silicon oxide and in the oxidising gas and of the oxidising species in the silicon oxide. The concentrations that play a role are the electron concentrations at the silicon oxide surface  $C_{\rm e,s}$ and at the  $Si-SiO_2$  interface  $C_{e,i}$ , the oxidising species concentrations at the silicon oxide surface  $C_{\text{H}_2\text{O},s}$  and at the Si-SiO<sub>2</sub> interface  $C_{\text{H}_2\text{O},i}$ and the reaction product concentrations at the silicon oxide surface  $C_{\mathcal{O}_i\mathcal{H}_i^{\mathrm{b-}},\mathrm{s}}$  and the  $\mathrm{Si}\text{-}\mathrm{SiO}_2$  interface  $C_{\mathcal{O}_i\mathcal{H}_i^{\mathrm{b-}},\mathrm{i}}$ . The flux of reaction product due to diffusion from the silicon oxide surface into the oxidising gas is included, because due to the production of the reaction product at both the interface and the surface, it is possible that the interface concentration may exceed the surface concentration, resulting in out-diffusion of the reaction product. This definitely occurs for thick oxides when tunnelling is negligible.

The different fluxes are described with the following formulas:

$$F_{\rm I,s} = k_{\rm I} C_{\rm e,s} C_{\rm H_2O,s}$$

(3.3)

$$F_{I,i} = k_I C_{e,i} C_{H_2O,i}$$

(3.4)

$$F_{\rm II} = k_{\rm II} C_{\rm O_i, H_i^{\rm b-}, i}$$

(3.5)

$$F_{{\rm O_i H_j^{b^-}, o}} = D_{{\rm O_i H_j^{b^-}, o}} \frac{C_{{\rm O_i H_j^{b^-}, s}} - C_{{\rm O_i H_j^{b^-}, i}}}{x_{\rm o}} \tag{3.6}$$

$$F_{\mathcal{O},\mathcal{H}_{i}^{b-},g} = D_{\mathcal{O},\mathcal{H}_{i}^{b-},g} C_{\mathcal{O},\mathcal{H}_{i}^{b-},s}$$

(3.7)

$$F_{\rm H_2O,o} = D_{\rm H_2O,o} \frac{C_{\rm H_2O,s} - C_{\rm H_2O,i}}{x_{\rm o}}$$

(3.8)

In these formulas,  $k_{\rm I}$  and  $k_{\rm II}$  are the reaction rate constants for reaction I and II,  $D_{{\rm O_i H_j^{b^-},o}}$  and  $D_{{\rm O_i H_j^{b^-},g}}$  are the effective diffusion constants for the reaction product in the silicon oxide and in the oxidation gas and  $D_{{\rm H_2O,o}}$  is the effective diffusion constant for water in silicon oxide. The reaction steps are considered to be of first order and steady-state conditions are imposed on the diffusion fluxes. The assumption of steady-state conditions, i.e. the total flux is constant is further translated in the following three formulas:

$$F_{\rm I,s} = F_{\rm O,H_i^{\rm b-},o} + F_{\rm O,H_i^{\rm b-},g}$$

(3.9)

$$F_{\rm I,i} = F_{\rm H_2O,o}$$

(3.10)

$$F_{\rm II} = F_{\rm I,i} + F_{\rm O,H_i^{\rm b-},o}$$

(3.11)

Combining the above equations for the fluxes with the equation for the oxidation rate:

$$\frac{dx_o}{dt} = \frac{F_{II}}{N} \tag{3.12}$$

results in:

$$\frac{dx_{\rm o}}{dt} = \frac{c_{\rm H_2O,s}}{N} \frac{{}^{D}_{\rm O_iH_j^{\rm b-},g}{}^{D}_{\rm H_2O,o}{}^{+k_{\rm I}D}_{\rm O_iH_j^{\rm b-},o}{}^{C_{\rm e,s}} + \frac{{}^{D}_{\rm H_2O,o}{}^{D}_{\rm O_iH_j^{\rm b-},o}}{x_{\rm o}} \left(1 + \frac{C_{\rm e,s}}{C_{\rm e,i}}\right)}{\left(1 + \frac{{}^{D}_{\rm H_2O,o}}{x_{\rm o}k_{\rm I}C_{\rm e,i}}\right) \left({}^{x_{\rm o}D}_{\rm O_iH_j^{\rm b-},g} + {}^{D}_{\rm O_iH_j^{\rm b-},o} \left(1 + \frac{{}^{D}_{\rm O_iH_j^{\rm b-},g}}{k_{\rm II}}\right)\right)}$$

$$(3.13)$$

where N represents the number of oxidant molecules incorporated in a unit volume of the silicon oxide layer. In the case that  $D_{\mathcal{O}_i\mathcal{H}_i^{\mathrm{b^-}},\mathrm{g}} \to 0$ ,

that is when out-diffusion of the reaction product does not occur, the above formula can be simplified to:

$$\frac{dx_{\rm o}}{dt} = \frac{C_{\rm H_2O,s}}{N} \left( k_{\rm I} C_{\rm e,s} + \frac{k_{\rm I} D_{\rm H_2O,o} C_{\rm e,i}}{D_{\rm H_2O,o} + x_{\rm o} k_{\rm I} C_{\rm e,i}} \right)$$

(3.14)

This formula describes a parallel oxidation process with a Deal-Grove component and an electron tunnelling stimulated component. For thick oxides, the tunnelling component will become negligibly small and the new model is exactly the Deal-Grove model, except that in the new model, the reaction between the oxidation species and silicon occurs in two successive steps using electron-stimulated dissociation.

### 3.5 Verification of the new model

The new oxidation model incorporates a number of parameters;  $k_{\rm I}$ ,  $k_{\rm II}$ ,  $D_{\rm O_i H_j^{\rm b-},o}$ ,  $D_{\rm O_i H_j^{\rm b-},g}$  and  $D_{\rm H_2O,o}$ . All five parameters will be described by an Arrhenius equation. Since the new model converges to the Deal-Grove model for thick oxides, the value of  $D_{\rm H_2O,o}$  and  $k_{\rm I}$  can be fitted to match the Deal-Grove parameters. The other three parameters are used as fitting parameters.

Figure 3.4 shows the result of fitting the measured oxidation data with the new model. It is clear from this figure that the new model does not provide a perfect fit. The curves for 950 °C can be nicely fit, but for lower oxidation temperatures, the model underestimates the silicon oxide thickness for the middle range of oxidation times. Still, the fit is reasonable and much better than the Deal-Grove model, taking into account the physically correct values. This is due to the addition of the two terms of backstream- and out-diffusion of the reaction product  $O_iH_j^{b-}$ . The model supplies a clear temperature and pressure dependence and is therefore also to be preferred over the Reisman and Wolters models.

A remarkable thing to note is that for the used parameter values, the tunnelling component does not play a role. This implies that there is room for improvement of the model. Tunnelling should play a role at least at low temperatures, to be able to provide the growth of for example native oxide at room temperature. The model incorporates the electron-stimulated dissociation only at the surface and the interface. An improvement can be expected when the electron-stimulated dissociation process takes place also inside the oxide. This will increase the importance of the electron tunnelling component and

Figure 3.4: Comparison of the measured data from chapter 2 with the oxidation model proposed here.

might be able to remove the underestimation of the model for the middle range oxidation times as well as the prediction of native oxide growth.

### 3.6 Conclusions

In this chapter, a new silicon oxidation model has been proposed, taking into account electron-stimulated dissociation of the oxidising species and the out-diffusion of the dissociated species. The model is able to fit the silicon oxidation data from chapter 2, but there is room for improvement.

# Chapter 4

# Device fabrication

### 4.1 Introduction

Hydrogen is abundantly available during the process of CMOS manufacturing. It is introduced during various processing steps where hydrogen-containing species are used at high ( $\geq 400\,^{\circ}$ C) temperature. Substitution of hydrogen with deuterium can in principle be done at any of these hydrogen-containing steps. However, care has to be taken that the deuterium introduced is not replaced by hydrogen during a subsequent processing step. This can occur during a high temperature step, when the already available hydrogen in the structure can diffuse, or during a hydrogen-containing step. These processing steps are the topic of this chapter.

In section 4.2 the general flow of processing steps during the manufacturing of a CMOS electronic circuit is described. In section 4.3 the processing steps which might be important for the final hydrogen and/or deuterium concentration in the device are highlighted, followed by a description of hydrogen diffusion through the several layers in a CMOS circuit in section 4.4. After this general description, the process flows of the specific devices used for the experiments described in chapters 5 and 6 are explored. For these experiments, two sets of devices have been used, fabricated at two different places. In section 4.5 the process flow of the devices fabricated at the University of Twente is treated followed by the process flow of the devices fabricated by Philips Research Leuven in section 4.6.

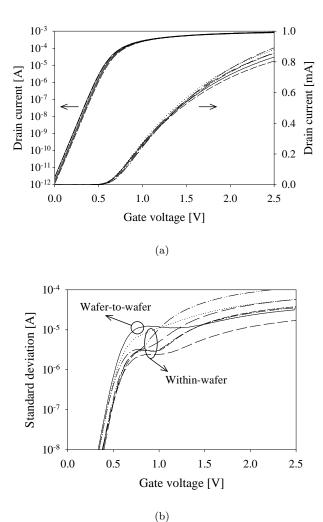

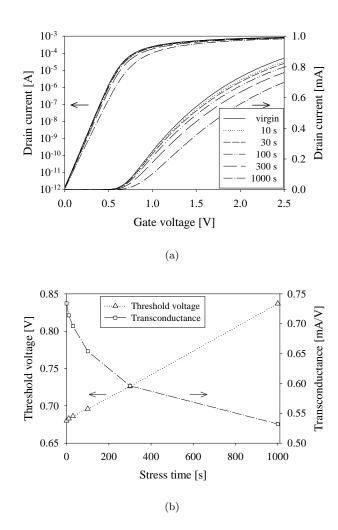

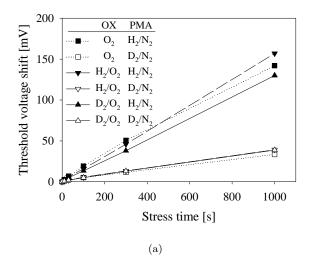

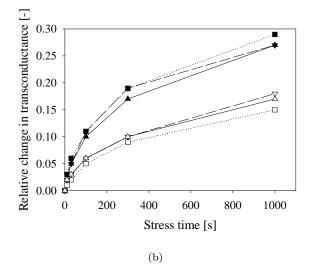

## 4.2 General CMOS manufacturing